无电容的3D DRAM,潜力无限

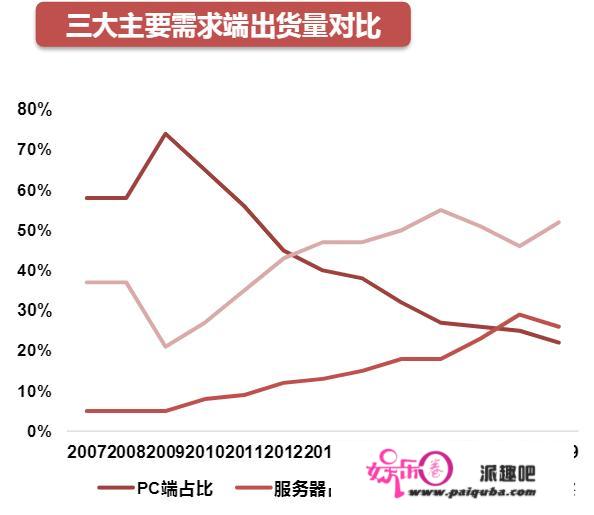

自1966年被IBM研究中心的Robert H. Dennard发明至今,动态随机存取存储器(DRAM)已经经过了数十年的发展,并成为存储器市场最大的细分领域,占据了58%的存储器市场规模。凭借着经济、可靠、高效等特点,DRAM被广泛运用于大容量的主存储器。2018年,DRAM的市场规模就已达到1000亿美元,根据IC Insights最新预测,预计到2026年全球DRAM市场规模甚至有望达到1219亿美元左右。然而技术的快速更迭让DRAM称霸存储市场的同时,也让它陷入了发展的瓶颈时期。在芯片小型化、集成化的发展趋势下,DRAM的缺点开始不断被“放大”,传统的DRAM已经难以满足当前的需求,在此背景下,人们开始把目光转向新型DRAM。3D 堆叠开启DRAM新未来当前,DRAM主要需求来源分别为PC端、移动端、服务器端,其中PC端占比12.6%,移动端占比37.6%,服务器占比 34.9%,三者占总需求近90%。从目前发展事态来看,PC端已经进入了存量替代市场,出货稳定,对DRAM的需求也趋于稳定。但随着5G热潮的到来,移动DRAM和服务器DRAM需求变得旺盛,DRAM迎来了“芯”拐点,智能手机带来的出货增长以及物联网、云服务、商用服务器、数据中心的强劲增长,成为拉动DRAM需求的主力军。此外,DRAM作为自动驾驶技术中不可或缺的一部分,车用DRAM也将成为未来的新增量。

图片来源:方正证券然而,庞大的需求端下,是人们不断增长的对高容量、高性能、小存储单元尺寸以及低功耗存储设备需求,这也使得DRAM在带宽和延迟方面的挑战更为紧迫,带宽指的是可以写入内存或可以从中读取的数据量,而延迟是对内存的请求与其执行之间的时间间隔。受限于传统计算机体系的冯-诺依曼架构,存储器带宽与计算需求之间的存储墙问题日益突出,成为当今计算中的最大问题之一。一般来说,计算机中的 DRAM 存储单元由单个晶体管和单个电容器制成,即所谓的 1T1C 设计。这种存储单元在写入时打开晶体管,电荷被推入电容器 (1) 或从电容器 (0) 去除;读取时则会提取并度量电荷。该系统速度超级快,价格便宜,并且功耗很小,但它也有一些缺点。DRAM作为一种易失性的、基于电容的、破坏性读取形式的存储器,在读取的时候会消耗电容器的电量,因此读取就要将该位写回到内存中。即使不进行读取,电荷最终也会通过晶体管从电容器中泄漏出来,从而随着时间的流逝而失去其明确定义的充电状态。虽然定期刷新可以保持数据,但这也意味着需要读取存储器的内容并将其重新写回。为了让DRAM更好地满足未来市场需求,业界也在不断地寻找新技术来突破目前的瓶颈,3D DRAM正是其中一个主流的技术方向。

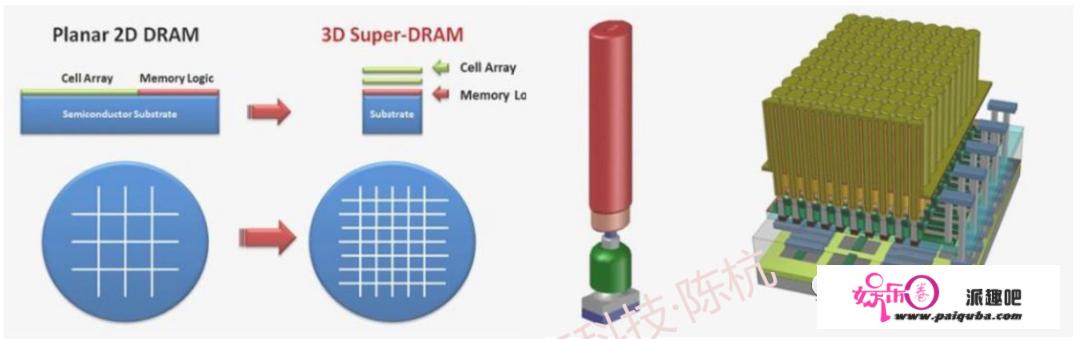

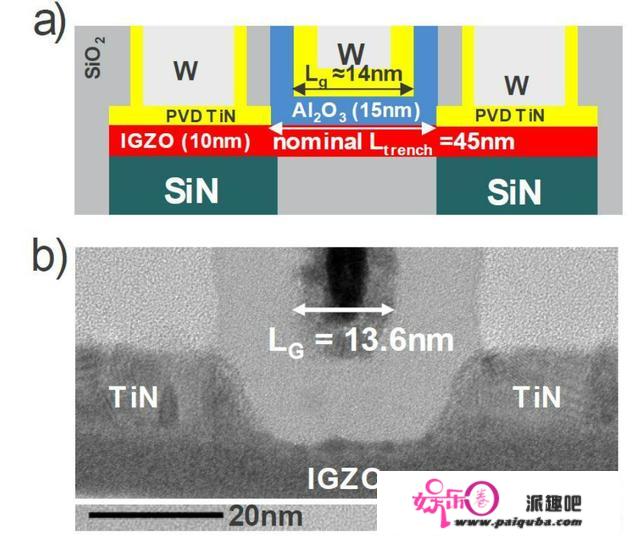

图片来源:方正证券据了解,3D DRAM是将存储单元(Cell)堆叠至逻辑单元上方以实现在单位晶圆面积上产出上更多的产量,从这方面来说,3D DRAM 可以有效解决平面DRAM最重要也最艰难的挑战,那就是储存电容的高深宽比。储存电容的深宽比通常会随着组件工艺微缩而呈倍数增加,也就是说,平面DRAM的工艺微缩会越来越困难。除了片晶圆的裸晶产出量增加外,使用3D堆栈技术也能因为可重复使用储存电容而有效降低 DRAM的单位成本。因此,可以认为DRAM从2D架构转向3D架构是未来的主要趋势之一。无电容IGZO,实现3D DRAM的候选者当前在存储器市场,能和DRAM“分庭抗礼”的NAND Flash早在2015年就已步入3D堆叠,并开始朝着100+层堆叠过渡,然而DRAM市场却仍处于探索阶段,为了使3D DRAM能够早日普及并量产,各大厂商和研究院所也在努力寻找突破技术。HBM(High Bandwidth Memory,高带宽存储器)技术可以说是DRAM从传统2D向立体3D发展的主要代表产品,开启了DRAM 3D化道路。它主要是通过硅通孔(Through Silicon Via, 简称“TSV”)技术进行芯片堆叠,以增加吞吐量并克服单一封装内带宽的限制,将数个DRAM裸片垂直堆叠,裸片之间用TVS技术连接。从技术角度看,HBM充分利用空间、缩小面积,正契合半导体行业小型化、集成化的发展趋势,并且突破了内存容量与带宽瓶颈,被视为新一代DRAM解决方案。除了HBM外,研究者们也开始在无电容技术方面下功夫,试图借此解决目前的难题。其实关于无电容,早有Dynamic Flash Memory、VLT技术、Z-RAM等技术出现,但日前,美国和比利时的独立研究小组IMEC在2021 IEDM 上展示了一款全新的无电容器 DRAM,这种新型的DRAM基于 IGZO(indium-gallium-zinc-oxide)可以完全兼容 300mm BEOL (back-end-of-line),并具有>103s保留和无限 (>1011) 耐久性。据介绍,这些结果是研究人员在为单个 IGZO 晶体管选择最佳集成方案后获得的,而这个最佳集成方案就是具有掩埋氧隧道和自对准接触的后栅极集成方案。使用这种架构后,IGZO TFT(thin-film transistors)的栅极长度可以缩小到前所未有的 14nm,同时仍然保持大于100s的保留。通过EOT(equivalent oxide thickness)缩放控制阈值电压 (Vt )、改善接触电阻和减小IGZO层厚度,可以进一步优化小栅极长度下的保持率。当后者的厚度减小到 5nm 时,甚至可以省略O2 中的氧隧道和退火步骤,从而大大简化了集成 *** 。

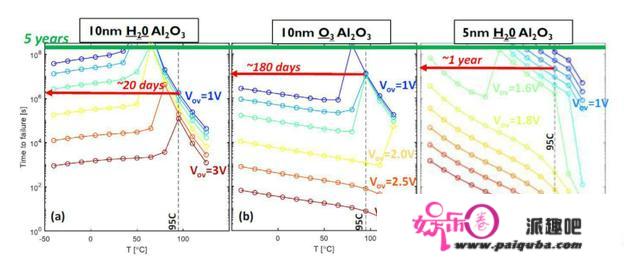

(a) 示意图和 (B) 具有氧隧道和 14nm 栅极长度的后栅极架构中单个 IGZO 晶体管的 TEM 图像其实,在2020 IEDM上,imec就首次展示过这种无电容DRAM,并在当时掀起了一阵热议。2020年消息显示,当时这款DRAM包括两个IGZO-TFTs并且没有存储电容,而这种2T0C(2晶体管0电容)DRAM架构还有望克服经典1T1C)(1晶体管1电容)DRAM 密度缩放的关键障碍,即小单元中 Si 晶体管的大截止电流尺寸,以及存储电容器消耗的大面积。但在去年的“概念性”演示中,IGZO TFT 并未针对最大保留率进行优化,并且缺少对耐久性(即故障前的读/写循环次数)的评估。而今年这款无电容DRAM显然在去年的基础上进行了改进,保留率和耐久性都有了提高。总的来说,今年新推出的新型DRAM 通过对基于 IGZO 的 DRAM架构和集成的改进,使2T0C DRAM 存储器具有>10 3保留、无限耐久性和栅极长度缩小至 14nm。更重要的是,这些突破性的成果都使得无电容IGZO-DRAM 成为实现高密度 3D DRAM 存储器的合适候选者。IGZO TFT的寿命挑战对于传统的2D技术来说,工艺制程不断微缩逼近10nm极限是不小的挑战。制程的微缩意味着光刻及蚀刻工艺所需的光罩数量不断提高,图案的分辨率很难得到保证。当工艺尺寸减小时,良率便无法得到控制,DRAM领域的bit growth从1994年至今一直处于下滑趋势,增速从70%降低至20%。工艺升级速度减缓,尺寸工艺减小的进程也遇到了阻碍。目前DRAM领域最为成熟的光刻技术是193nmDUV光刻机,其最大极限在大约10nm,而下一代13.5nmEUV光刻机是DRAM 工艺节点实现10nm以下突破的关键。引用此前一位网友的评论:“DRAM工艺不断改进,按照一代工艺一代设备,又到了不断加码买设备的时间节点了。”各大原厂纷纷有意引入分辨率更高的EUV光刻机来推动DRAM持续发展,但ASML 的EUV一年产能仅十几台,难以满足当前需求,而且价格也是极其昂贵。据了解,ASML亮相的新一代0.55NA EUV光刻机售价提高到19亿元,高昂的售价使得EUV经济效益低于DUV,同时如何将EUV技术投入量产也成为传统2D技术面临的难题之一。而对于IGZO TFT来说,寿命问题或许是其未来发展的一大挑战。目前为止,IGZO TFT 退化机制尚未被完全了解,因此缺乏用于预测基于 IGZO 的 DRAM 寿命的准确模型。针对这个问题,IMEC首次研究了栅极电介质对 IGZO TFT PBTI (positive bias temperature instability)的影响。IGZO 晶体管本质上是 n 型器件,这表明PBTI可能是主要的退化机制。PBTI 是Sin型MOSFET中众所周知的老化机制,会严重影响器件的性能和可靠性,通常表现为器件阈值电压的不期望偏移和漏极电流的降低。然而,大多数现有的IGZO TFT 可靠性评估都忽略了栅极电介质的影响。IMEC研究团队发现四种不同的机制在降解过程中起作用,每种机制具有不同的时间动力学和活化能。它们主要归因于栅极电介质中的电子捕获,以及在 PBTI 应力期间氢物质从栅极电介质释放到 IGZO 沟道。

基于不同栅极电介质的 IGZO TFT(具有 12 纳米厚的非晶 IGZO 膜)的失效时间目前,该研究团队已将这些多种退化机制组合成一个模型,从而可以预测目标操作条件下的 IGZO TFT 寿命,可用于提出优化来提高寿命。写在最后对于未来DRAM该怎么走,其实研究者们已经提供了很多技术方向,但是目前均处于探索阶段。基于PBTI的模型能否真的提升IGZO设备寿命;IGZO TFT 又能否使DRAM走向3D堆叠;3D堆叠是否真的可以为DRAM发展开辟新路径,而这一切都需要市场来检验。但可以肯定的是,随着这些突破性技术的发展,DRAM 远未走到生命尽头,未来或将继续称霸存储器市场。*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2892内容,欢迎关注。

晶圆|集成电路|设备|汽车芯片|存储|台积电|AI|封装