DRAM(动态随机存储器)的原理及芯片实现

什么是DRAM?

DRAM(动态随机存储器)在日常生活中还有一个亲热称号叫内存条,操纵电容贮存电荷几来存储数据,需要按时刷新电路克制电容漏电问题,读写速 度比SRAM慢,常用于容量大的主存储器,如计算机、智妙手机、办事器内存等。

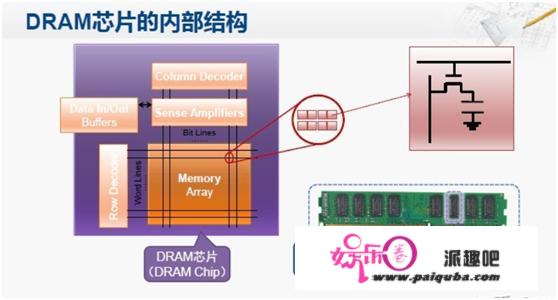

DRAM内部构造

DRAM实物模组

DRAM汗青与开展:早期存储器的开展史

1942年,世界上第一台电子数字计算机ATANASOFF-BERRY COMPUTER(ABC)降生,利用再生电容 磁鼓存储器存储数据。

1946年,随机存取存储器(RAM)问世,静电记忆管能在实空管内利用静电荷存储大约4000字节数据。

1947年,延迟线存储器被用于改进雷达声波。延迟线存储器是一种能够重刷新的存储器,仅能挨次存取 。同年磁芯存储器降生,那是随机存取存储器(RAM)的早期版本。

1951年,磁带初次被用于计算机上存储数据,在UNIVAC计算机上做为次要的I/O设备,称为UNIVACO ,那就是商用计算机史上的第一台磁带机。

1956年,世界上第一个硬盘驱动器呈现在了IBM的RAMAC 305计算机中,标记着磁盘存储时代的起头。 该计算机是第一台供给随机存取数据的计算机,同时还利用了磁鼓和磁芯存储器。

1965年,美国物理学家Russell创造了只读式光盘存储器(CD-ROM),1966年提交了专利申请。 1982 年,索尼和飞利浦公司发布了世界上第一部商用CD音频播放器CDP-101,光盘起头普及。

1966年,DRAM被创造。IBM Thomas J. Watson 研究中心的Robert H. Dennard创造了动态随机存取 存储器(DRAM),并于1968年申请了专利。

1970年,Intel公司推出第一款商用DRAM芯片Intel 1103,彻底倾覆了磁存储手艺。DRAM的呈现处理 了磁芯存储器体积庞大,运行速度慢,存储密度低及能耗较高档问题。

DRAM分类

DRAM次要能够分为DDR(Double Data Rate)系列、LPDDR(Low Power Double Data Rate)系列和GDDR(Graphics Double Data Rate)系列、HBM系列。

DDR是内存模块中使输出增加一倍的手艺,是目前支流的内存手艺。LPDDR具有低功耗的特征,次要应用于便携设备。GDDR一般会婚配利用高性能显卡配合利用,适用于具有高带宽图形计算的范畴。

云计算、大数据的鼓起,办事器的数据容量和处置速度在不竭进步,鞭策了DDR手艺的晋级 迭代,目前市场上支流手艺标准为DDR4和LPDDR4,DDR5手艺即将进入商用范畴。

DRAM将来手艺及造程

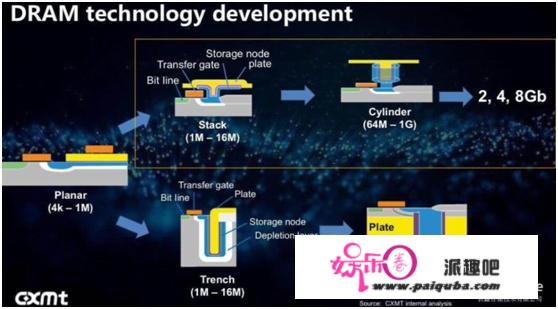

DRAM从2D架构转向3D架构是将来的次要趋向之一。3D DRAM是将存储单位(Cell)堆叠至逻辑单位 上方以实如今单元晶圆面积上产出上更多的产量,那里次要通过改动电容设想实现,从平面电容到深槽电容再到堆叠电容,相较于通俗的平面DRAM,3D DRAM能够有效降低 DRAM的单元成本。

其他开展途径:接纳铁电质料的设想电容(ferro capacitor)以耽误DRAM位元格贮存电荷的时间耽误。 具有改善DRAM的材料保留时间(retention time),减小刷新的承担、快速开启或封闭低功耗形式、实 现更低的备用功耗,以及进一步鞭策DRAM的规模化等长处。利用低漏电流堆积的薄膜晶体管(thin-film transistor),例如氧化铟镓锌,来代替DRAM位元格内的硅基晶体管,以大幅降低贮存单位的面积。

DRAM存储单位电路蚀刻剖面演变

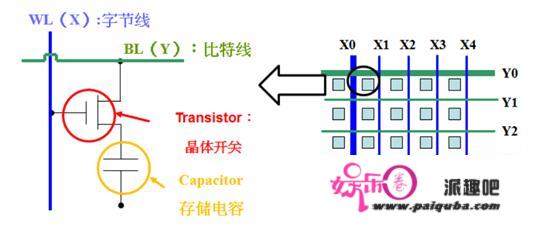

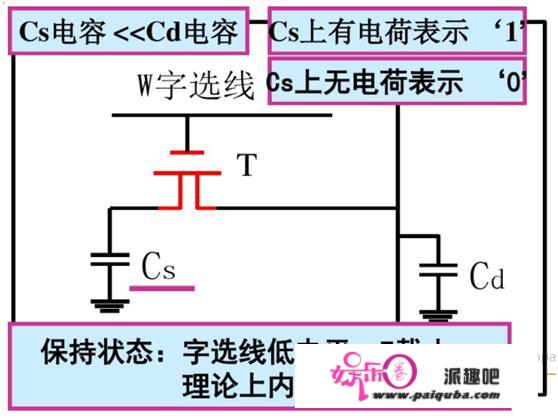

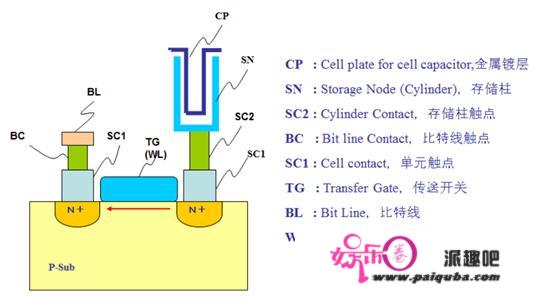

DRAM存储单位构造

内存芯片根本单位构造(DRAM Memory Cell Circuit)

WL(X):字节线(Word Line),X地址寻址线(Row Address);

BL(Y):比特线(Bit Line),Y地址寻址线(Column Address)和数据收支输出线(Data In/Out);

Transistor : 金属氧化物半导体场效应(MOS)晶体管开关;

Capacitor: 电荷储能单位即电容。

备注:内存芯片中每个单位都有以字节线和比特线组合的独登时址。以2016年支流4GB单面8芯片内存条为例,每粒内存芯片有4G个独登时址。

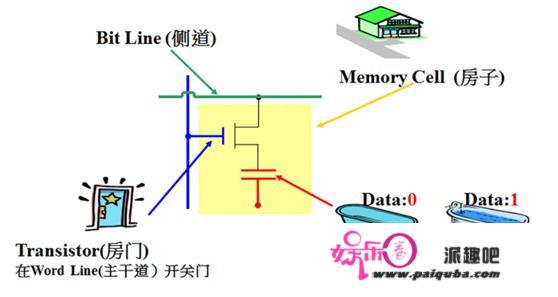

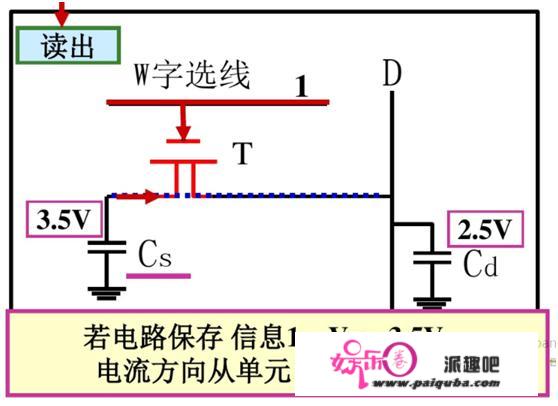

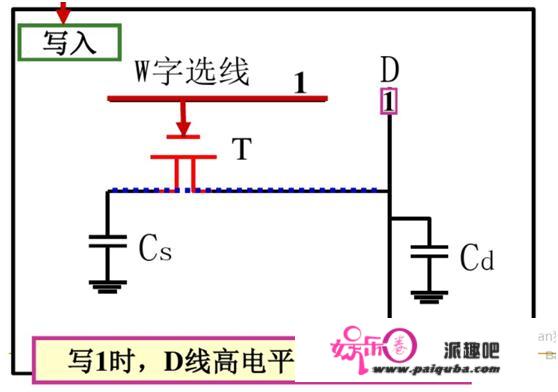

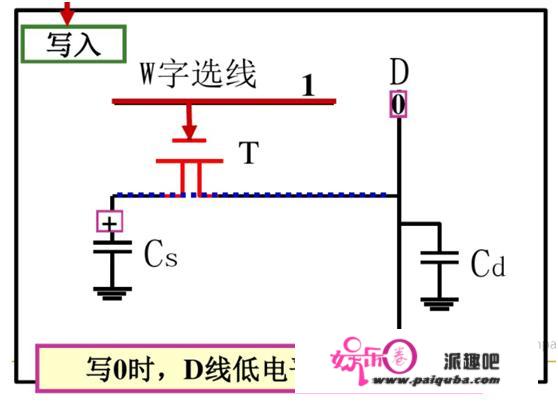

DRAM存储单位电路读写原理

存储单位电路

DRAM芯片工做原理

最早、最简单也是最重要的一款DRAM 芯片是Intel 在1979 年发布的2188,那款芯片是16Kx1 DRAM 18 线DIP 封拆。“16K x 1”的部门意思告诉我们那款芯片能够存储16384个bit 数据,在统一个期间能够同时停止1bit 的读取或者写入操做。

DRAM2188芯片引脚图

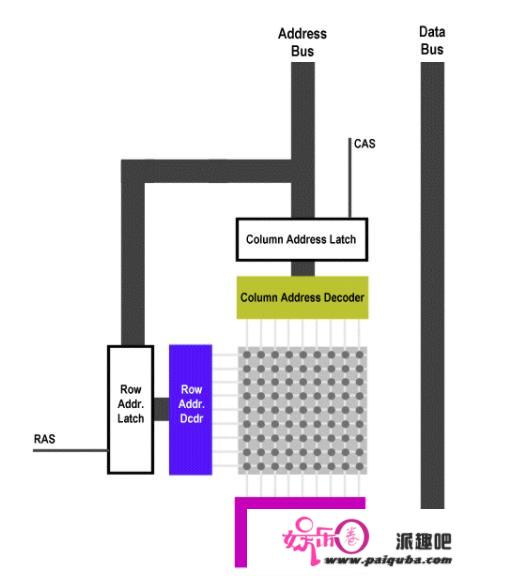

2188内部架构

DRAM2188内部有/RAS(Row Address Strobe:行地址脉冲选通器)引脚控造的行地址门闩线路(Row Address Latch)和由/CAS(Column Address Strobe:列地址脉冲选通器)引脚控造的列地址门闩线路(ColumnAddress Latch)。

存储(读取)流程图

1)通过地址总线将行地址传输到地址引脚2)/RAS 引脚被激活,如许行地址被放入到行地址选通电路中3) 行地址解码器( Row Address Decoder)选择准确的形式然后送到传感放大器( sense amps)4)/WE 引脚被确定不被激活,所以DRAM 晓得它不会停止写入操做5)列地址通过地址总线传输到地址引脚6)/CAS 引脚被激活,如许列地址被放入到列地址选通电路中7)/CAS 引脚同样还具有/OE 引脚的功用,所以那个时候Dout 引脚晓得需要向外输出数据。8) /RAS 和/CAS 都不被激活,如许就能够停止下一个周期的数据操做了。其实DRAM 写入的过程和读取过程是根本一样的,所以若是你实的理解了上面的过程就能晓得写入过程了,所以那里就不赘述了。(只要把第4 步改为/WE 引脚被激活就能够了)。

DRAM存储单位电路的半导体芯片实现

存储单位单路芯片剖面图

存储电容的蚀刻流程:

以深槽电容器造程为例分为3个阶段;

(1)深槽蚀刻造程 (2)电容介电层及上下基板造程 (3)埋藏式毗连带BS的构成

深槽刻蚀造程

介电层上下基板造程

BS构成造程

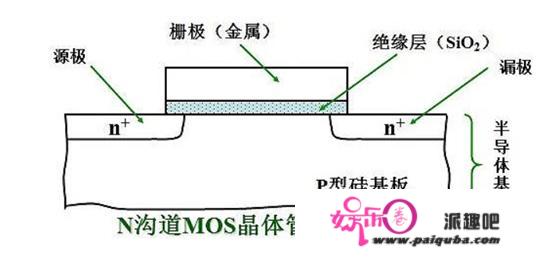

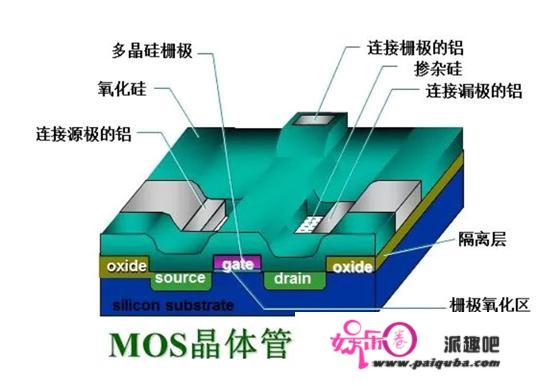

MOS管工艺简介:

那就是一个 NMOS 的构造简图,一个看起来很简单的三端元器件。详细的造造过程就像搭建积木一样,在必然的地基(衬底)上根据设想一步步“盖”起来,大致要颠末以下步调:

(1)单晶硅切片,研磨,抛光 (2)清洗后,再生长一层二氧化硅 (3)一次光刻 (4)扩散工艺掺杂 (5)二次光刻 (6)实空镀铝 (7)反刻电极 (8)合金 (9)挑选管芯焊盘,键合引线 (10)中测 (11)封拆 (12)末测

MOS管剖面构造图

MOS管立体芯片图

我来回答